任意波形發生器在雷達、通信領域中發揮著重要作用,但目前任意波形發生器大多使用靜態存儲器。這使得在任意波形發生器工作頻率不斷提高的情況下,波形的存儲深度很難做得很大,從而不能精確地表達復雜信號。本文介紹的基于動態存儲器(SDRAM)的設計能有效解決這一問題,并詳細討論了一種簡化SDRAM控制器的設計方法。

1 任意波形發生器的總體方案

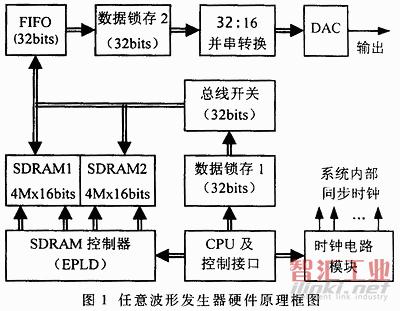

工作頻率、分辨率和存儲長度是任意波形發生器最關鍵的三個性能參數。高的工作頻率意味著高的輸出信號頻率和帶寬,高的分辨率通常意味著高的信噪比,而存儲長度決定了信號的精確程度。下面介紹的方案是筆者實際開發的一款任意波形發生器/卡(如圖1所示),它的工作頻率為300MHz,分辨率為14位,存儲長度為8M字,現已得到了廣泛地應用。

該電路主要有兩種工作狀態:寫數據狀態和讀數據狀態。下面簡單描述其工作過程。

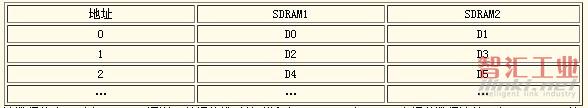

寫數據狀態:CPU根據所要設計的波形計算波形數據,并轉換成14位的無符號數;打開總線開關,屏蔽FIFO操作,在SDRAM控制器的配合下,將波形數據通過接口電路交替寫入SDRAM1和SDRAM2中,即SDRAM1中依次存放數據0,2,4,6...;SDRAM2中依次存放數據1,3,5,7...(如表1所示)。

讀數據狀態:開啟FIFO通道,關閉總線開關以斷開SDRAM與CPU之間的數據連接;在SDRAM控制器的控制下,將SDRAM1/2中的數據同時(并行)讀出;經過FIFO的緩沖得到連續的數據流,再經32位向16位的并串轉換,將數據速率提升2倍后,供給DAC進行數-模轉換,即可得到所編輯的信號。

圖1中用兩片SDRAM并行工作,是因單片SDRAM不可能提供300MSPS的數據流。實際使用的器件是K4S641632C-TC60,工作時鐘為166MHz。FIFO緩存SDRAM的輸出數據,將突發數據流轉換成連續數據流,使得在SDRAM處于刷新狀態時,仍能維持正常的數據輸出。實際使用的器件是兩片并行工作的IDT72V263L6PF,寫入時鐘為166MHz,讀出時鐘為150MHz。并串轉換的作用是提升數據的速率,在DAC器件內部完成,筆者采用具有良好動態性能的AD9755AST。CPU及控制接口是一個基于PC的ISA設備,可改進為PCI設備;時鐘電路用來產生166MHz和150MHz的同步時鐘。下面重點研究SDRAM控制器的設計,它是本系統的主要特色之一。

2 SDRAM控制器的設計

2.1 SDRAM的主要特點

與靜態存儲器(SRAM)相比,SDRAM的容量大(通常是幾倍至幾十倍的關系);與DDR SDRAM或RDRAM相比,它的控制又相對簡單,因而它依然是大容量存儲器工程項目的良好選擇。下面描述的幾個重要基本概念反映了它的主要特點。

行列地址:SDRAM的地址是行列復用的,此舉有效減少了芯片的引腳。

預充電:讀寫操作只對預充電過的行有效。也就是說,在數據讀寫操作跨行時,需要先進行至少一次的預充電操作。

自動刷新:眾所周知,只要是動態RAM,就存在刷新問題,SDRAM也不例外。通常每隔64ms需要將所有存儲單元刷新一遍。

自刷新:當需要保留芯片內的數據,而暫時又不需要操作時,可以設置芯片進入自刷新狀態。

工作模式寄存器:控制SDRAM工作方式的寄存器。

2.2 SDRAM的狀態流程

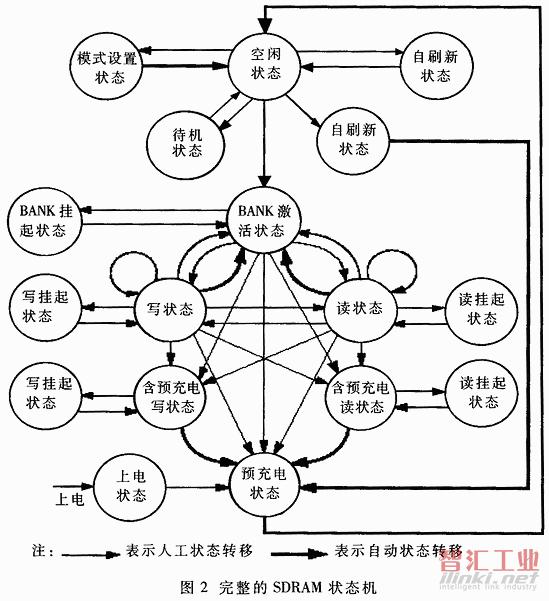

SDRAM的完整狀態機由17個狀態構成,且狀態轉移是非隨機的(如圖2所示)。正是如此眾多的狀態及其復雜的轉換關系,導致SDRAM的控制較為復雜。

需要特別說明的是,SDRAM的狀態轉移有自動轉移與人工轉移之分(圖2中以粗細箭頭加以區別)。自動轉移在當前狀態結束后立即進入下一個狀態;而人工轉移在當前狀態結束后即停留在當前狀態,只有一條當前狀態允許的命令才能進入下一個狀態。

可以想象,自行設計如此復雜的控制流程絕非易事。值得慶幸的是,在大多數應用中并不需要完備的狀態機。下面討論一種簡化的SDRAM狀態機。

2.3 簡化的狀態流程

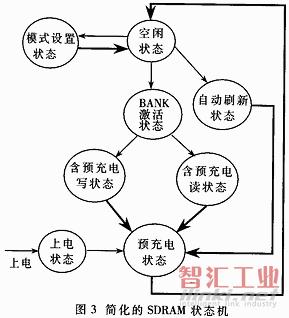

根據任意波形發生器的特點,對SDRAM的功能進行了以下簡化:

(1)省略隨機存取功能,固定為順序讀寫;

(2)省略待機、自刷新、普通讀/寫功能;

(3)省略所有的掛起功能;

(4)工作模式固定為突發式讀、單個式寫;

(5)數據延時固定為3個時鐘周期;

(6)刷新模式只使用自動刷新方式,器件空閑時即處于連續的自動刷新狀態;

(7)器件僅在上電后進行一次初始化,不能改變工作模式;

(8)突發方式固定為順序方式,突發長度固定為整頁;

(9)只使用帶預充電的讀/寫指令;在每次讀/寫操作完成后,即啟動一個自動刷新周期。

經過以上簡化的狀態機如圖3所示。

2.4 SDRAM控制器的EPLD實現

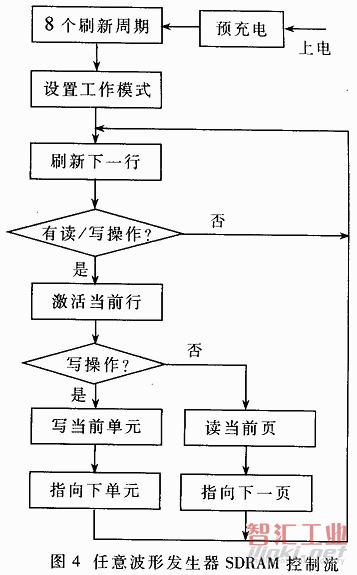

為了實現上述簡化的SDRAM控制功能,采用一片ALTERA公司生產的EPLD器件MAX7256ATC144-6。圖4是任意波形發生器SDRAM控制流示意圖。由于具體編程要涉及許多細節問題,在此不做贅述,其主要功能如下:

(1)通過ISA總線,實現與CPU的接口,接收波形數據和讀命令;

(2)上電自動初始化;

(3)生成23位(8M字存儲器空間)的線性地址,并按行列復用的方式輸出;

(4)生成SDRAM的控制信號,完成讀、寫和自動刷新功能;

(5)控制FIFO,以解決SDRAM刷新和波形長度不是頁長度的倍數問題。

雖然完全應用SDRAM確實比較復雜,但只要本著“夠用就行”的原則,對其功能進行合理的簡化,設計出具有特殊需求、適用于特定條件的SDRAM控制器是完全可行的。目前,筆者已將基于SDRAM的任意波形發生器應用到多個研發項目中。

(審核編輯: 智匯小新)

分享